Overview Clock Distribuito

Nel bus di campo EtherCAT, lo slave è tecnologicamente più avanzato del master; anche perché monta un hardware, che permette di gestire il suo timer interno al nanosecondo. Quando il Master EtherCAT parte, viene settato l’orologio a zero di tutti gli slave EtherCAT. Quando il frame arriva al primo slave, questo setta il timer interno per ottenere sempre il frame Ethercat allo stesso tempo (ad es. 1ms). Il suo timer interno viene poi trasmesso a tutti gli altri slave che supportano il clock distribuito. In questo modo anche se il master non è proprio preciso nell’emissione del frame, questo viene “aggiustato” dagli slave. Questo sistema ha effetto sul jitter (+/-) del frame.

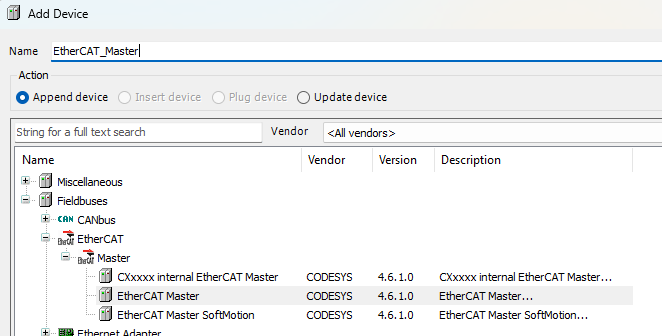

Aggiunta del device EtherCAT Master

Aggiungere un nuovo device partendo dal Device principale:

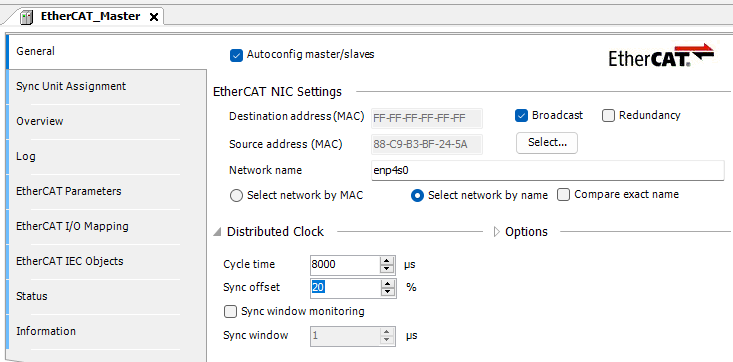

Sync offset

Parametro per impostare il tempo di ritardo tra la base tempi DC dell’EtherCAT Slave e l’inizio ciclo del PLC. Il valore predefinito è 20%. Questo tempo è attivo contemporaneamente per tutti gli slave con DC. Un offset del 20% significa che l’interruzione del timer nello slave EtherCAT avviene il 20% prima del successivo ciclo IEC.

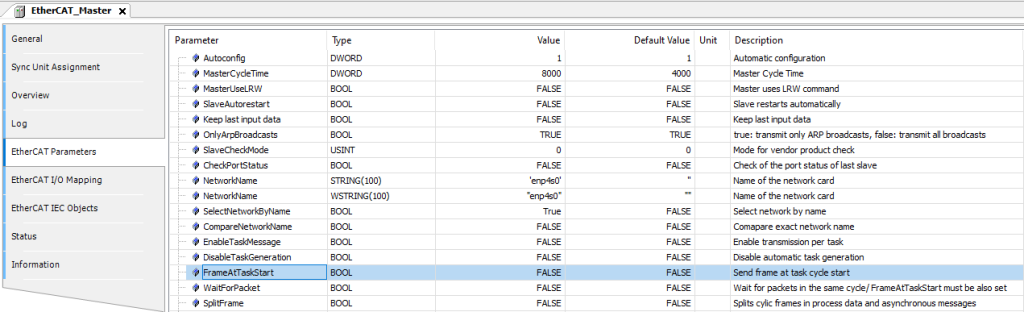

EtherCAT Master

Quando si inserisce il dispositivo EtherCAT_Master il parametro “FrameAtTaskStart” è settato a FALSE:

Questo settaggio ha un impatto sull’invio del frame EtherCAT che, in questo caso, viene spedito alla fine del ciclo PLC. Se, ad esempio, stiamo utilizzando un Sync offset al 20%, il ciclo del PLC può richiedere l’80% del tempo di ciclo del bus meno il tempo di ritardo nel runtime, e questo senza che il Master non metta più in tempo i dati di processo attuali sul bus (partendo dal presupposto che lo slave EtherCAT attende i nuovi dati esattamente con interruzione della sincronizzazione).

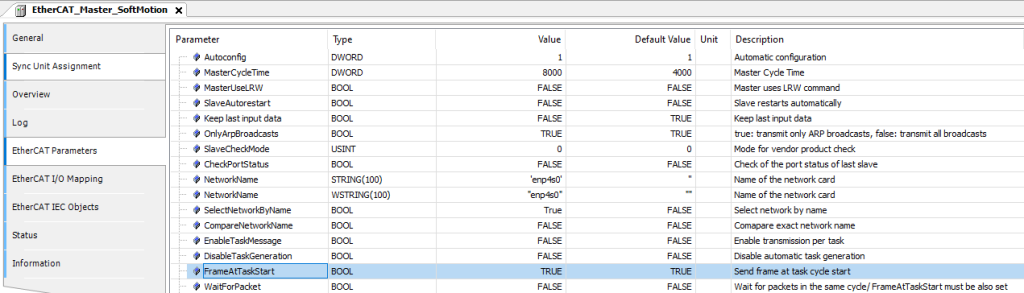

EtherCAT Master SoftMotion

Quando si inserisce il dispositivo EtherCAT_Master_SoftMotion il parametro “FrameAtTaskStart” è settato a TRUE. Valore predefinito quando si utilizza CODESYS SoftMotion:

Questo settaggio ha un impatto sull’invio del frame EtherCAT che, in questo caso, viene spedito all’avvio del task Cycle Bus. Il frame viene preparato un ciclo prima. Questo vuol dire che, se il nostro Cycle Bus è 1ms, il frame EtherCAT è in ritardo di 1ms. Questo non è importante anche perché tutto il sistema sarà in ritardo di 1ms.

Per il programma del controllore, quasi il 100% del ciclo è sempre disponibile. Qui l’offset Sync determina solo quando i dati EtherCAT del master vengono scambiati da e verso gli slave rispetto alla base temporale dello slave EtherCAT.

Lascia un commento